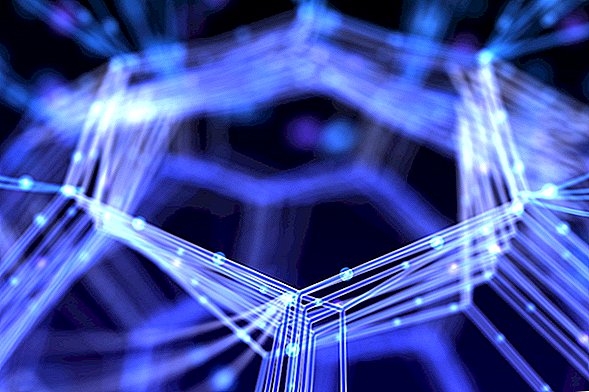

Een nieuw type 3D-computerchip dat twee geavanceerde nanotechnologieën combineert, zou de snelheid en energie-efficiëntie van processors drastisch kunnen verhogen, aldus een nieuwe studie.

De chips van vandaag scheiden het geheugen (dat gegevens opslaat) en logische circuits (die gegevens verwerken), en gegevens worden heen en weer geschakeld tussen deze twee componenten om bewerkingen uit te voeren. Maar vanwege het beperkte aantal verbindingen tussen geheugen- en logische circuits, wordt dit een groot knelpunt, vooral omdat van computers wordt verwacht dat ze met steeds grotere hoeveelheden gegevens omgaan.

Eerder werd deze beperking gemaskeerd door de effecten van de wet van Moore, die zegt dat het aantal transistors dat op een chip past elke twee jaar verdubbelt, met een bijbehorende prestatieverbetering. Maar toen chipfabrikanten fundamentele fysieke limieten bereikten voor hoe kleine transistors kunnen worden, is deze trend vertraagd.

De nieuwe prototype-chip, ontworpen door ingenieurs van Stanford University en het Massachusetts Institute of Technology, pakt beide problemen tegelijkertijd aan door geheugen- en logische circuits op elkaar te leggen in plaats van naast elkaar.

Dit maakt niet alleen efficiënt gebruik van de ruimte, maar vergroot ook het oppervlak voor verbindingen tussen de componenten dramatisch, aldus de onderzoekers. Een conventionele logische schakeling zou een beperkt aantal pinnen aan elke rand hebben om gegevens over te dragen; de onderzoekers waren daarentegen niet beperkt tot het gebruik van randen en waren in staat om verticale draden die van de logische laag naar de geheugenlaag lopen dicht opeen te pakken.

"Met afzonderlijk geheugen en computergebruik is een chip bijna twee steden met veel inwoners, maar er zijn maar heel weinig bruggen tussen hen", vertelde studieleider Subhasish Mitra, een professor in elektrotechniek en informatica aan Stanford, aan WordsSideKick.com. 'Nu hebben we niet alleen deze twee steden bij elkaar gebracht, we hebben nog veel meer bruggen gebouwd, zodat het verkeer tussen hen veel efficiënter kan verlopen.'

Bovendien gebruikten de onderzoekers logische circuits die waren opgebouwd uit koolstofnanobuis-transistors, samen met een opkomende technologie genaamd resistief willekeurig toegankelijk geheugen (RRAM), die beide veel energiezuiniger zijn dan siliciumtechnologieën. Dit is belangrijk omdat de enorme energie die nodig is om datacenters te runnen een andere grote uitdaging vormt voor technologiebedrijven.

"Om de volgende 1000 keer betere computerprestaties te krijgen op het gebied van energie-efficiëntie, waardoor dingen met een zeer laag energieverbruik worden uitgevoerd en tegelijkertijd de dingen heel snel laten lopen, is dit de architectuur die je nodig hebt," zei Mitra.

Hoewel beide nieuwe nanotechnologieën inherente voordelen hebben ten opzichte van conventionele, op silicium gebaseerde technologie, zijn ze ook een integraal onderdeel van de 3D-architectuur van de nieuwe chip, aldus de onderzoekers.

De reden waarom de huidige chips 2D zijn, is omdat het vervaardigen van siliciumtransistors op een chip temperaturen vereist van meer dan 1.800 graden Fahrenheit (1.000 graden Celsius), waardoor het onmogelijk is om siliciumcircuits op elkaar te leggen zonder de onderste laag te beschadigen, aldus de onderzoekers .

Maar zowel koolstof nanobuis transistors als RRAM zijn gefabriceerd bij koeler dan 392 graden F (200 graden C), zodat ze gemakkelijk op silicium kunnen worden gelaagd zonder de onderliggende circuits te beschadigen. Dit maakt de aanpak van de onderzoekers ook compatibel met de huidige technologie voor het maken van chips, zeiden ze.

Het stapelen van veel lagen op elkaar kan mogelijk leiden tot oververhitting, zei Mitra, omdat de bovenste lagen ver verwijderd zijn van de heatsinks aan de basis van de chip. Maar, voegde hij eraan toe, dat probleem moet relatief eenvoudig zijn om rond te werken, en de verhoogde energie-efficiëntie van de nieuwe technologie betekent dat er in de eerste plaats minder warmte wordt gegenereerd.

Om de voordelen van het ontwerp te demonstreren, bouwde het team een prototype gasdetector door een extra laag op koolstof nanobuisjes gebaseerde sensoren bovenop de chip toe te voegen. Door de verticale integratie was elk van deze sensoren rechtstreeks verbonden met een RRAM-cel, waardoor de snelheid waarmee gegevens konden worden verwerkt aanzienlijk werd verhoogd.

Deze gegevens werden vervolgens overgebracht naar de logische laag, die een machine learning-algoritme implementeerde waarmee het onderscheid kon maken tussen de dampen van citroensap, wodka en bier.

Dit was echter slechts een demonstratie, zei Mitra, en de chip is zeer veelzijdig en bijzonder geschikt voor het soort data-zware, diepe neurale netwerkbenaderingen die de huidige kunstmatige intelligentie-technologie ondersteunen.

Jan Rabaey, hoogleraar elektrotechniek en informatica aan de University of California in Berkeley, die niet bij het onderzoek betrokken was, zei het daarmee eens te zijn.

"Deze structuren zijn met name geschikt voor alternatieve, op leren gebaseerde rekenparadigma's zoals door de hersenen geïnspireerde systemen en diepe neurale netten, en de benadering van de auteurs is absoluut een geweldige eerste stap in die richting", vertelde hij aan MIT News.